इलेक्ट्रिकल कॅपेसिटन्स ही इलेक्ट्रोस्टॅटिक्सच्या मूलभूत संकल्पनांपैकी एक आहे. हा शब्द विद्युत शुल्क जमा करण्याच्या क्षमतेचा संदर्भ देतो. तुम्ही एकाच कंडक्टरच्या कॅपेसिटन्सबद्दल बोलू शकता, तुम्ही दोन किंवा अधिक कंडक्टरच्या सिस्टीमच्या कॅपेसिटन्सबद्दल बोलू शकता. शारीरिक प्रक्रिया समान आहेत.

सामग्री

कॅपेसिटन्सशी संबंधित मूलभूत संकल्पना

जर कंडक्टरला चार्ज q मिळाला असेल, तर त्यावर संभाव्य φ उद्भवतो. ही क्षमता भूमिती आणि वातावरणावर अवलंबून असते - भिन्न कंडक्टर आणि परिस्थितींसाठी, समान शुल्क भिन्न क्षमता निर्माण करेल. पण φ नेहमी q च्या प्रमाणात असते:

φ=Cq

गुणांक C आणि त्याला विद्युत क्षमता म्हणतात. जर आपण अनेक कंडक्टरच्या प्रणालीबद्दल बोलत आहोत (सामान्यतः दोन), जेव्हा एका कंडक्टरला (क्लॅडिंग) चार्ज दिला जातो, तेव्हा संभाव्य फरक किंवा व्होल्टेज U असतो:

U=Cq, म्हणून C=U/q

कॅपॅसिटन्सची व्याख्या संभाव्य फरक आणि चार्जच्या संभाव्य फरकाचे गुणोत्तर म्हणून केली जाऊ शकते. SI मधील क्षमतेचे एकक म्हणजे फॅराड (ते फॅराड म्हणायचे). 1 F = 1 V/1 Cl.दुसऱ्या शब्दांत, ज्या प्रणालीमध्ये 1 कूलॉम्बचा चार्ज 1 व्होल्टच्या संभाव्य फरकास जन्म देतो त्याची क्षमता 1 फॅराड असते. 1 फॅरड हे खूप मोठे मूल्य आहे. सराव मध्ये, फ्रॅक्शनल व्हॅल्यूज - पिकोफॅरॅड्स, नॅनोफॅरॅड्स, मायक्रोफॅराड्स - सर्वात सामान्यतः वापरली जातात.

सराव मध्ये, हे कनेक्शन एका सेलपेक्षा जास्त डायलेक्ट्रिक ब्रेकडाउन व्होल्टेज सहन करू शकणार्या बॅटरीसाठी परवानगी देते.

कॅपेसिटर क्षमतेची गणना

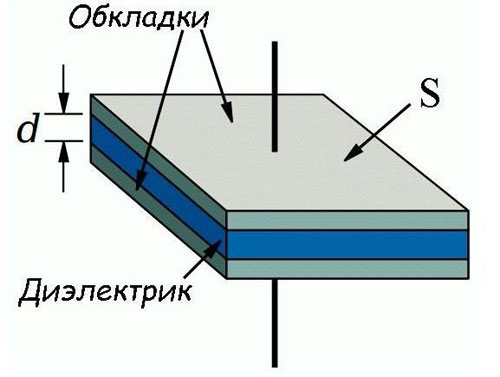

सराव मध्ये, सामान्यीकृत विद्युत क्षमता असलेले घटक म्हणून, सर्वात सामान्यतः वापरले जातात कॅपेसिटर, दोन सपाट कंडक्टर (टर्मिनल्स), डायलेक्ट्रिकद्वारे विभक्त केलेले. अशा कॅपेसिटरच्या विद्युत क्षमता मोजण्याचे सूत्र खालीलप्रमाणे आहे:

C=(S/d)*ε*ε0

कुठे:

- सी कॅपेसिटन्स आहे, एफ;

- S हे इन्सर्टचे क्षेत्रफळ आहे, sq.m;

- d हे कव्हर्समधील अंतर आहे, m;

- ε0 - विद्युत स्थिरांक, स्थिरांक, 8.854*10−12 F/m;

- ε - डायलेक्ट्रिक परमिटिव्हिटी, डायमेंशनलेस व्हॅल्यू.

यावरून हे समजणे सोपे आहे की कॅपॅसिटन्स कव्हर्सच्या क्षेत्रफळाच्या थेट प्रमाणात आणि कंडक्टरमधील अंतराच्या व्यस्त प्रमाणात आहे. ज्या सामग्रीसह कव्हर वेगळे केले जातात त्या सामग्रीचा देखील कॅपेसिटन्स प्रभावित होतो.

कॅपॅसिटन्स निर्धारित करणाऱ्या प्रमाणांचा कॅपेसिटरच्या चार्ज साठवण्याच्या क्षमतेवर कसा परिणाम होतो हे समजून घेण्यासाठी, तुम्ही सर्वाधिक संभाव्य कॅपेसिटन्स असलेले कॅपेसिटर तयार करण्यासाठी एक मानसिक प्रयोग करू शकता.

- आपण windings क्षेत्र वाढवण्याचा प्रयत्न करू शकता. यामुळे डिव्हाइसच्या आकारात आणि वजनात नाटकीय वाढ होईल. डाईलेक्ट्रिकसह थरांचा आकार कमी करण्यासाठी, ते गुंडाळले जातात (ट्यूबमध्ये, सपाट ब्रिकेट इ.).

- दुसरा मार्ग म्हणजे कव्हर्समधील अंतर कमी करणे. कंडक्टर एकमेकांच्या अगदी जवळ ठेवणे नेहमीच शक्य नसते, कारण डायलेक्ट्रिक लेयर कव्हर्समधील विशिष्ट संभाव्य फरक सहन करण्यास सक्षम असणे आवश्यक आहे.जाडी जितकी लहान असेल तितकी इन्सुलेटिंग गॅपची विद्युत शक्ती कमी असेल. जर आपण हा मार्ग वापरला तर असा एक क्षण येईल जेव्हा अशा कॅपेसिटरचा व्यावहारिक उपयोग अर्थहीन होईल - ते केवळ अत्यंत कमी व्होल्टेजवर कार्य करू शकते.

- डायलेक्ट्रिक इलेक्ट्रिकल पारगम्यता वाढवणे. हा मार्ग सध्याच्या उत्पादन तंत्रज्ञानाच्या विकासावर अवलंबून आहे. इन्सुलेटिंग सामग्रीमध्ये केवळ उच्च पारगम्यता मूल्यच नाही तर चांगले डायलेक्ट्रिक गुणधर्म देखील असणे आवश्यक आहे आणि आवश्यक वारंवारता श्रेणीमध्ये त्याचे पॅरामीटर्स टिकवून ठेवणे आवश्यक आहे (जसे कॅपेसिटर चालते ती वारंवारता वाढते, डायलेक्ट्रिक वैशिष्ट्ये कमी होतात).

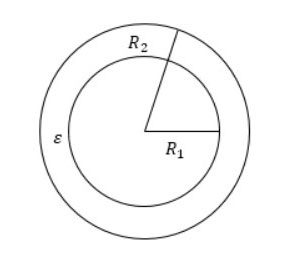

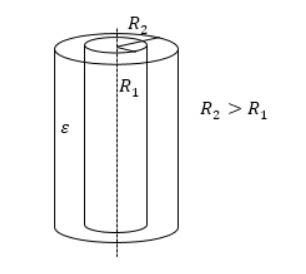

गोलाकार किंवा दंडगोलाकार कॅपेसिटर काही विशेष किंवा संशोधन प्रतिष्ठापनांमध्ये वापरले जाऊ शकतात.

गोलाकार कॅपेसिटरची क्षमता सूत्राद्वारे मोजली जाऊ शकते

C=4*π*ε0 *R1R2/(R2-R1)

जेथे R ही गोलांची त्रिज्या आहे आणि π=3.14.

बेलनाकार कॅपेसिटर डिझाइनसाठी, कॅपेसिटन्सची गणना खालीलप्रमाणे केली जाते:

C=2*π*ε*ε0 *l/ln(R2/R1)

l ही सिलेंडरची उंची आहे आणि R1 आणि R2 त्यांची त्रिज्या आहेत.

तत्त्वानुसार, दोन्ही सूत्रे फ्लॅट कॅपेसिटरच्या सूत्रापेक्षा भिन्न नाहीत. कॅपेसिटन्स नेहमी टर्मिनल्सच्या रेखीय परिमाण, त्यांच्यामधील अंतर आणि डायलेक्ट्रिकच्या गुणधर्मांद्वारे निर्धारित केले जाते.

मालिका आणि समांतर मध्ये कॅपेसिटर कनेक्ट करणे

कॅपेसिटर कनेक्ट केले जाऊ शकतात मालिकेत किंवा समांतर, नवीन वैशिष्ट्यांसह एक संच तयार करणे.

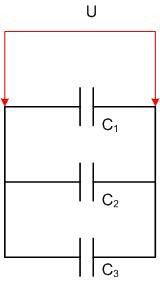

समांतर कनेक्शन

कॅपेसिटर समांतर जोडलेले असल्यास, परिणामी बॅटरीची एकूण कॅपॅसिटन्स त्याच्या घटकांच्या सर्व कॅपेसिटन्सच्या बेरजेइतकी असते. जर बॅटरीमध्ये समान डिझाईनचे कॅपेसिटर असतील, तर ते सर्व प्लेट्सचे क्षेत्रफळ जोडेल असे मानले जाऊ शकते. या प्रकरणात, बॅटरीच्या प्रत्येक घटकावरील व्होल्टेज समान असेल आणि शुल्क वाढेल. समांतर जोडलेल्या तीन कॅपेसिटरसाठी:

- U=U1=यू2=यू3;

- q=q1+q2+q3;

- C=C1+C2+C3.

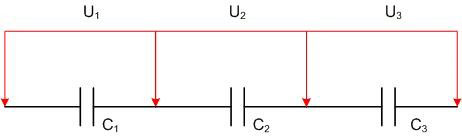

मालिकेतील कनेक्शन

मालिकेत कनेक्ट केल्यावर, प्रत्येक कॅपेसिटन्सचे शुल्क समान असेल:

q1=q2=q3=q

एकूण व्होल्टेजच्या प्रमाणात वितरीत केले जाते कॅपेसिटरच्या कॅपेसिटन्सपर्यंत:

- यू1=q/C1;

- यू2=q/C2;

- यू3= q/C3.

जर सर्व कॅपेसिटर समान असतील तर प्रत्येकावर समान व्होल्टेज येतो. एकूण क्षमता खालीलप्रमाणे आढळते:

C=q/( U1+U2+U3), म्हणून 1/C=( U1+U2+U3)/q=1/C1+1/С2+1/С3.

अभियांत्रिकीमध्ये कॅपेसिटरचे अनुप्रयोग

विद्युत उर्जेचे संचयक म्हणून कॅपेसिटर वापरणे अर्थपूर्ण आहे. अशा प्रकारे, ते लहान संचयित ऊर्जेमुळे इलेक्ट्रोकेमिकल स्त्रोतांशी (गॅल्व्हॅनिक बॅटरी, कॅपेसिटर) स्पर्धा करू शकत नाहीत आणि डायलेक्ट्रिकमधून चार्ज गळतीमुळे जलद स्व-डिस्चार्ज. परंतु त्यांची ऊर्जा दीर्घ काळासाठी साठवून ठेवण्याची आणि नंतर ती जवळजवळ त्वरित देण्याची क्षमता मोठ्या प्रमाणावर वापरली जाते. हा गुणधर्म फोटोग्राफीसाठी फ्लॅश दिवे किंवा लेझरच्या उत्तेजनासाठी दिव्यामध्ये वापरला जातो.

रेडिओ अभियांत्रिकी आणि इलेक्ट्रॉनिक्समध्ये कॅपेसिटर खूप सामान्य आहेत. कॅपेसिटर रेझोनंट सर्किट्समध्ये सर्किट्सच्या वारंवारता-धारण घटकांपैकी एक म्हणून वापरले जातात (दुसरा घटक इंडक्टन्स आहे). AC घटकाला अडकवल्याशिवाय थेट करंट बाहेर ठेवण्याची कॅपेसिटरची क्षमता देखील वापरली जाते. एका स्टेजच्या डीसी मोड्सचा दुसऱ्या टप्प्यावरील प्रभाव दूर करण्यासाठी अॅम्प्लीफायरच्या टप्प्यांचे विभाजन करण्यासाठी असा अनुप्रयोग सामान्य आहे. उच्च-क्षमतेचे कॅपेसिटर वीज पुरवठ्यामध्ये स्मूथिंग फिल्टर म्हणून वापरले जातात. इतर असंख्य कॅपेसिटर ऍप्लिकेशन्स देखील आहेत जिथे त्यांचे गुणधर्म उपयुक्त ठरतात.

काही व्यावहारिक कॅपेसिटर डिझाइन

सराव मध्ये विविध प्रकारचे फ्लॅट कॅपेसिटर डिझाइन वापरले जातात. डिव्हाइसची रचना त्याची वैशिष्ट्ये आणि अनुप्रयोग निर्धारित करते.

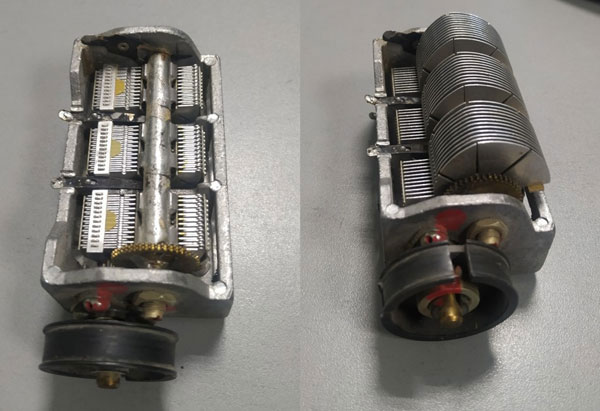

व्हेरिएबल कॅपेसिटर

व्हेरिएबल कॅपेसिटरचा एक सामान्य प्रकार (AC कॅपॅसिटर) मध्ये हवेने विभक्त केलेल्या जंगम आणि स्थिर प्लेट्सचा ब्लॉक किंवा घन इन्सुलेटर असतो.जंगम प्लेट्स एका अक्षाभोवती फिरतात, आच्छादित क्षेत्र वाढवतात किंवा कमी करतात. जंगम युनिट मागे घेतल्यावर, इंटरइलेक्ट्रोड अंतर अपरिवर्तित राहते, परंतु प्लेट्समधील सरासरी अंतर देखील वाढते. इन्सुलेटरचा डायलेक्ट्रिक स्थिरांक देखील अपरिवर्तित राहतो. कव्हरचे क्षेत्रफळ आणि त्यांच्यामधील सरासरी अंतर बदलून कॅपेसिटन्स समायोजित केले जाते.

ऑक्साइड कॅपेसिटर

या प्रकारच्या कॅपेसिटरला इलेक्ट्रोलाइटिक कॅपेसिटर असे म्हणतात. यात इलेक्ट्रोलाइटमध्ये भिजलेल्या पेपर डायलेक्ट्रिकद्वारे विभक्त केलेल्या फॉइलच्या दोन पट्ट्या असतात. पहिली पट्टी एक कव्हर आणि दुसरी इलेक्ट्रोलाइट म्हणून काम करते. डायलेक्ट्रिक हा धातूच्या एका पट्टीवर ऑक्साईडचा पातळ थर असतो आणि दुसरी पट्टी वर्तमान संग्राहक म्हणून काम करते.

कारण ऑक्साईडचा थर अतिशय पातळ आहे आणि इलेक्ट्रोलाइट त्याच्या जवळ आहे, मध्यम आकारासह बरीच मोठी क्षमता मिळवणे शक्य होते. यासाठी किंमत कमी ऑपरेटिंग व्होल्टेज आहे - ऑक्साईड लेयरमध्ये उच्च विद्युत शक्ती नसते. ऑपरेटिंग व्होल्टेज वाढते म्हणून, कॅपेसिटरचा आकार लक्षणीय वाढवावा लागतो.

दुसरी समस्या अशी आहे की ऑक्साईडमध्ये एक-मार्गी चालकता असते, म्हणून अशा कॅपेसिटरचा वापर केवळ ध्रुवीयतेचे पालन करून डीसी सर्किटमध्ये केला जातो.

आयनिस्टर

वर दर्शविल्याप्रमाणे, वाढीच्या पारंपारिक पद्धती कॅपेसिटर नैसर्गिक मर्यादा आहेत. म्हणूनच, वास्तविक यश म्हणजे आयनिस्टर्सची निर्मिती.

जरी हे उपकरण कॅपेसिटर आणि बॅटरी दरम्यानचे मध्यवर्ती मानले जाते, तरीही ते मूलत: कॅपेसिटर आहे.

दुहेरी विद्युत थर वापरून कॉइलमधील अंतर कमालीचे कमी केले जाते. विरुद्ध शुल्क असलेल्या आयनांचे थर थर म्हणून काम करतात. फोम सच्छिद्र सामग्रीमुळे कव्हर्सच्या पृष्ठभागाचे क्षेत्रफळ मोठ्या प्रमाणात वाढवणे शक्य आहे.परिणामी, शेकडो फॅराड्सपर्यंत क्षमतेसह सुपरकॅपेसिटर मिळवणे शक्य आहे. अशा उपकरणांचा अंतर्निहित रोग म्हणजे कमी ऑपरेटिंग व्होल्टेज (सामान्यतः 10 व्होल्ट्सच्या आत).

तंत्रज्ञानाचा विकास स्थिर नाही - बर्याच भागातील दिवे द्विध्रुवीय ट्रान्झिस्टरने बदलले आहेत, त्या बदल्यात, एकध्रुवीय ट्रायोड्सने बदलले आहेत. सर्किट डिझाईनमध्ये शक्य असेल तेथे इंडक्टर्सची सुटका होत आहे. आणि कॅपेसिटर दुसऱ्या शतकासाठी त्यांची स्थिती सोडत नाहीत, लेडेन जारचा शोध लागल्यापासून त्यांची रचना मूलभूतपणे बदललेली नाही आणि त्यांच्या कारकीर्दीच्या समाप्तीची शक्यता पाळली जात नाही.

संबंधित लेख: