トリガーはデジタル要素であり、1 つの状態に切り替わる双安定デバイスであり、外部信号が取り除かれても、この状態を無期限に維持できます。第 1 レベルの論理要素 (AND-NE、OR-NE など) から構成され、第 2 レベルの論理デバイスを参照します。

実際には、トリガーは、個別のパッケージ内の超小型回路として、または大規模集積回路 (LSI) またはプログラマブル ロジック マトリックス (PLM) 内の要素として利用できます。

トリガーの分類とタイミングの種類

トリガーは、次の 2 つの大きなクラスに分けられます。

- 非同期;

- 同期 (クロック)。

それらの基本的な違いは、デバイスの最初のカテゴリでは、出力信号のレベルが入力での信号の変化と同時に変化することです。同期トリガの場合、状態は、この目的のために提供された入力にクロック信号が存在する場合にのみ変化します。この目的のために、文字 C (クロック) で示される特別な出力が用意されています。ストローブ同期要素のタイプに応じて、次の 2 つのクラスに分けられます。

- 動的;

- 静的。

最初のタイプでは、クロックパルスのエッジ(立ち上がりエッジ)または立ち下がりエッジが現れた瞬間の入力信号の構成に応じて、出力レベルが変化します(特定のタイプのトリガーによって異なります)。クロック エッジ (減衰) の出現の間に任意の信号を入力に供給することができ、トリガー状態は変化しません。 2 番目のバージョンはクロッキング レベルを変更しませんが、Clock 入力に 1 または 0 が存在することは、クロッキングの兆候です。次のように分類される複雑なトリガー デバイスもあります。

- 定常状態の数 (基本要素の 2 ではなく、3 つ以上)。

- レベル数 (3 つ以上);

- その他の特徴。

複雑な要素は、特定のデバイスでは使用が制限されています。

トリガーの種類とその動作原理

トリガーにはいくつかの基本的なタイプがあります。相違点に入る前に、共通点に注意する必要があります。電源が投入されると、どのデバイスの出力も任意の状態に設定されます。これが回路全体の動作にとって重要な場合は、プリセット回路を用意する必要があります。最も単純なケースでは、これは初期状態設定信号を形成する RC 回路です。

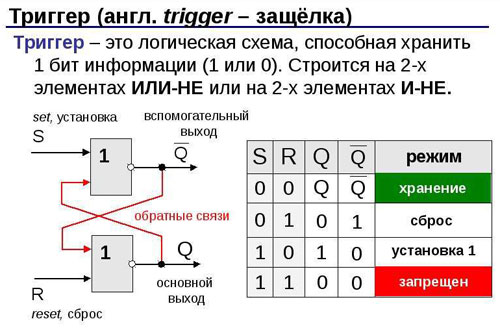

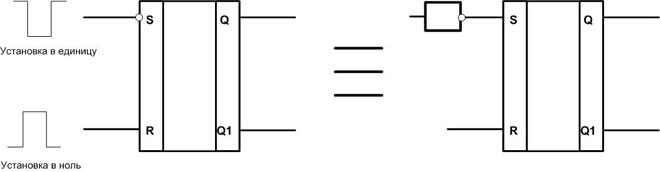

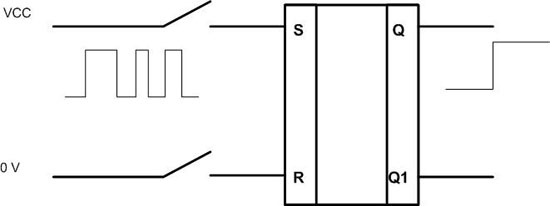

RS トリガー

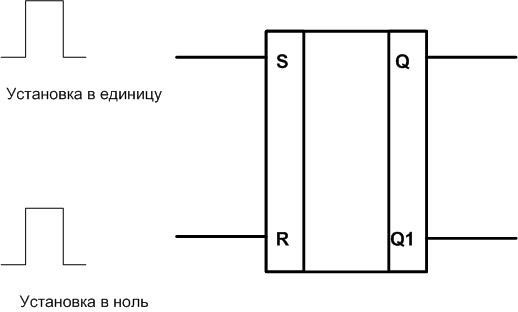

非同期双安定デバイスの最も一般的なタイプは、RS トリガーです。これは、状態 0 と 1 の設定が別々のトリガーを指します。これには 2 つの入力があります。

- S - セット(セット);

- R - リセット。

直接出力 Q があり、反転出力 Q1 にすることもできます。そのロジック レベルは常に Q の逆です。これは、回路を設計するときに役立ちます。

入力 S に正のレベルが適用されると、出力 Q は論理 1 に設定されます (反転出力がある場合は、レベル 0 になります)。その後、設定入力の信号は好きなように変更できます - 出力レベルは影響を受けません。 1 つが R 入力に表示される限り。これにより、トリガーが状態 0 (反転ピンで 1) に設定されます。リセット入力の信号の変化は、要素のそれ以降の状態には影響しません。

重要! 両方の入力に論理 1 がある場合のバリアントは禁止されています。トリガーは任意の状態に設定されます。回路設計時には、このような状況を避ける必要があります。

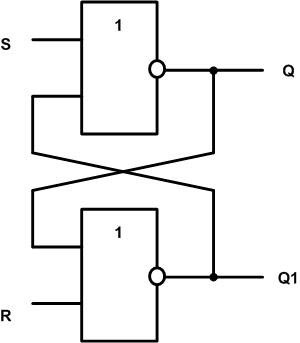

RS トリガーは、一般的に使用されるデュアル入力 I-NE 要素に基づいて構築できます。この方法は、従来のチップだけでなく、プログラマブル アレイ内でも実行できます。

一方または両方の入力を反転できます。これは、これらのピンでは、トリガーが高レベルではなく低レベルの出現によって制御されることを意味します。

RS Trigger を 2 つの I-NE 入力要素で構築すると、両方の入力が反転され、論理ゼロの供給によって制御されます。

RS トリガーのゲート バージョンがあります。追加の C 入力があります。次の 2 つの条件が満たされると、切り替えが発生します。

- セットまたはリセット入力に高レベルが存在する。

- クロック信号の存在。

このような要素は、たとえばトランジェントの終了時など、切り替えを遅らせる必要がある場合に使用されます。

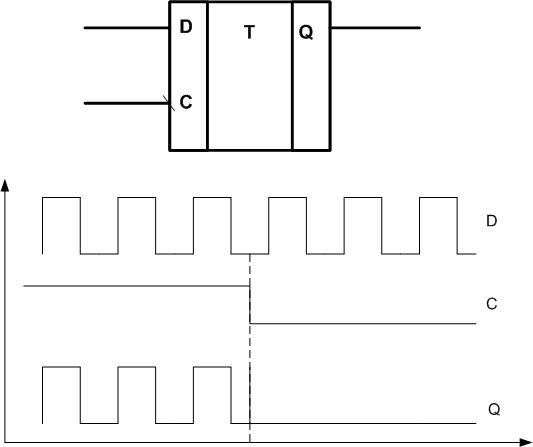

Dトリガー

D トリガー (「トランスペアレント トリガー」、「ラッチ」) は、入力 C でクロックされる同期デバイスのカテゴリに属します。データ D (データ) の入力もあります。機能面では、デバイスは1つの入力による情報の受信を伴うトリガーに属します。

クロック入力に論理 1 がある限り、出力 Q の信号はデータ入力の信号を繰り返します (透過モード)。ストローブ レベルが 0 になるとすぐに、出力 Q のレベルはドロップ (ラッチ) の時点と同じままです。このようにして、いつでも入力レベルを入力にロックできます。エッジ トリガーの D トリガーもあります。ストローブの正のエッジで信号をラッチします。

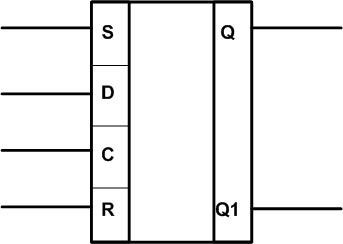

実際には、2 種類の双安定デバイスを 1 つのチップに組み合わせることができます。たとえば、D トリガーと RS トリガーです。この場合、セット/リセット入力が優先されます。論理ゼロの場合、エレメントは通常の D トリガーのように動作します。少なくとも 1 つの入力が高レベルの場合、入力 C および D の信号に関係なく、出力は 0 または 1 に設定されます。

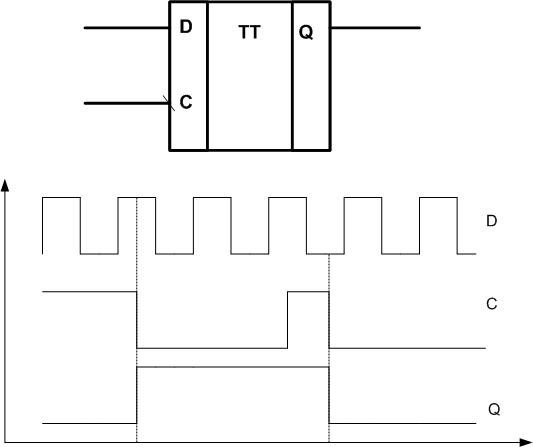

D トリガーの透過性は、必ずしも便利な機能ではありません。これを回避するために、ダブル エレメント (フリップフロップ トリガー) が使用され、文字 TT で示されます。最初のトリガーは、入力信号を出力に送る通常のラッチです。 2 番目のトリガーはメモリ要素です。どちらも単一のストロボによってクロックされます。

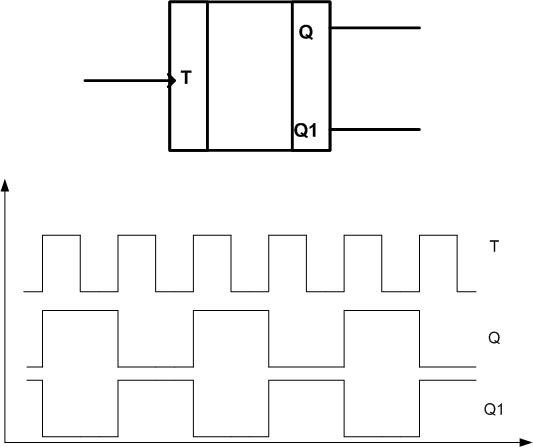

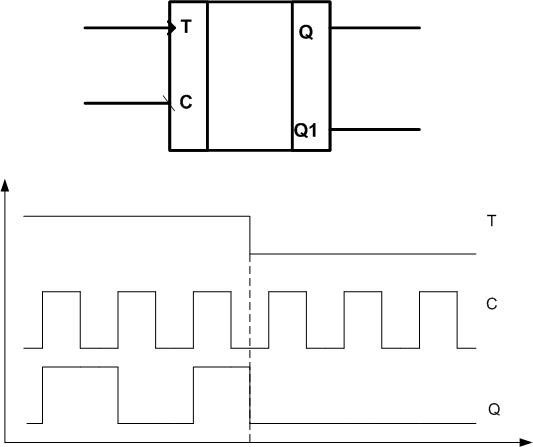

Tトリガー

T トリガーは可算双安定要素です。その動作のロジックは単純で、次の論理値が入力に来るたびに状態が変化します。入力にパルス信号を加えると、出力周波数は入力周波数の 2 倍になります。反転出力では、信号は直接信号に対して逆位相になります。

これが非同期 T トリガーのしくみです。同期バージョンもあります。パルス信号がクロック入力に適用され、論理 1 がピン T に存在する場合、要素は非同期のものと同じように動作します - 入力周波数を半分に分割します。 T ピンが論理ゼロの場合、Q 出力はゲートの存在に関係なくローに設定されます。

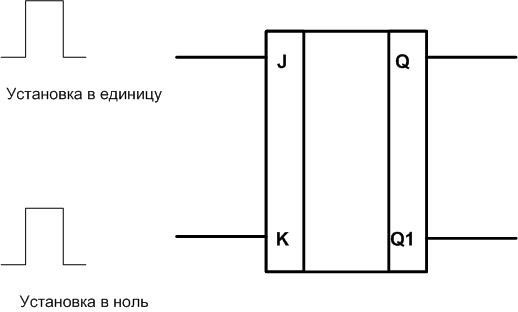

JKトリガー

JKトリガー

この双安定要素は、普遍的なカテゴリに属します。入力によって個別に制御できます。 JK トリガーのロジックは、RS 要素のロジックと似ています。 J (ジョブ) 入力は、出力を 1 に設定するために使用されます。ピン K (キープ) のハイ レベルは、出力をゼロにリセットします。 RS トリガーとの基本的な違いは、2 つの制御入力に 1 が同時に出現することが禁止されていないことです。この場合、要素の出力はその状態を反対に変更します。

ジョブ出力とキープ出力が接続されている場合、JK トリガーは非同期カウント T トリガーになります。結合された入力に蛇行が適用されると、出力は周波数の半分になります。RS 要素と同様に、JK トリガーのクロック バージョンがあります。実際には、使用されるのは主にこのタイプのゲート要素です。

実用

外部信号を取り除いても記録情報を保持するトリガーの性質により、1ビット容量のメモリセルとして使用できます。行列は、バイナリ状態を格納するために単一の要素から構築できます。これは、スタティック ランダム アクセス メモリ (SRAM) を構築するために使用される原則です。このメモリの特徴は、追加のコントローラを必要としない単純な回路です。そのため、SRAM はコントローラや PLC で使用されます。しかし、書き込み密度が低いため、PC やその他の強力なコンピューティング システムでこのような行列を使用することはできません。

分周器としてのトリガーの使用については、上記で説明しました。双安定要素をチェーンに接続して、さまざまな分割係数を得ることができます。同じチェーンをパルスカウンタとして使用できます。これを行うには、中間要素から各時点での出力の状態を読み取る必要があります。最初の要素の入力に到達したパルス数に対応するバイナリ コードを取得します。

使用されるトリガーのタイプに応じて、カウンターは同期または非同期になります。順次コードから並列コードへのコンバーターにも同じ原理が使用されますが、ここではゲート可能な要素のみが使用されます。トリガーは、デジタル遅延線やその他のバイナリ要素を構築するためにも使用されます。

RS トリガーは、レベル ラッチ (コンタクト バウンス サプレッサー) として使用されます。メカニカル スイッチ (ボタン、スイッチ) がロジック レベル ソースとして使用されている場合、チャタリング効果により、押されたときに 1 つではなく多くの信号が形成されます。 RS-trigger はこれにうまく対処します。

双安定デバイスの応用分野は広い。彼らの助けを借りて解決できるタスクの範囲は、特に非標準ソリューションの分野では、設計者の想像力に大きく依存します。

関連記事: