觸發器是一種數字元件,一種雙穩態器件,可以切換到一種狀態,即使外部信號被移除,也可以無限期地保持在這種狀態。它由一級邏輯元素(AND-NE、OR-NE 等)構成,指代二級邏輯設備。

在實踐中,觸發器可以作為單獨封裝中的微電路使用,也可以作為大型集成電路 (LSI) 或可編程邏輯矩陣 (PLM) 中的元件使用。

觸發分類和時序類型

觸發器分為兩大類:

- 異步;

- 同步(時鐘)。

它們之間的根本區別在於,在第一類設備中,輸出信號電平的變化與輸入信號的變化同時發生。對於同步觸發,只有在為此目的提供的輸入端存在時鐘信號時,狀態才會改變。為此提供了一個特殊的輸出,用字母 C(時鐘)表示。根據選通同步元件的類型分為兩類:

- 動態的;

- 靜止的。

在第一種類型中,輸出電平的變化取決於時鐘脈衝的邊沿(前沿)或下降沿出現時的輸入信號配置(取決於觸發的具體類型)。任何信號都可以在時鐘沿(衰減)出現之間饋送到輸入,觸發狀態不會改變。第二個版本不改變時鐘電平,但時鐘輸入上出現 1 或 0 是時鐘的標誌。也有復雜的觸發裝置按以下分類:

- 穩態數量(3 個或更多,而基本元素為 2 個);

- 級別數(也超過 3 個);

- 其他特徵。

複雜元素在特定設備中的用途有限。

觸發器的類型及其操作原理

有幾種基本類型的觸發器。在我們討論差異之前,我們應該注意一個共性:當施加電源時,任何設備的輸出都會設置為任意狀態。如果這對電路的整體運行至關重要,則必須提供預設電路。在最簡單的情況下,這是一個形成初始狀態設置信號的 RC 電路。

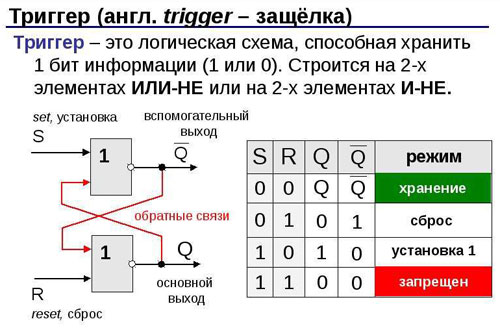

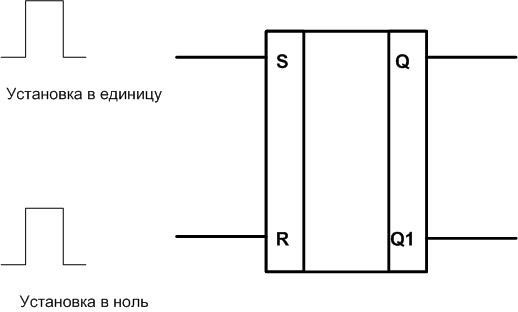

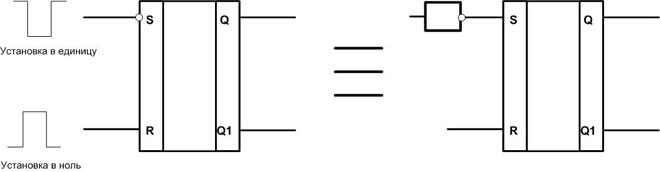

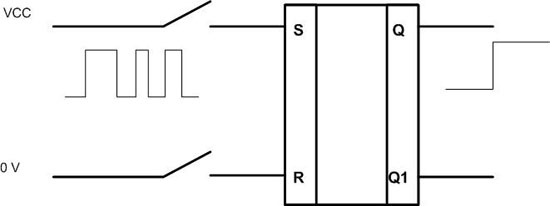

RS 觸發器

最常見的異步雙穩態器件類型是 RS 觸發器。它指的是具有單獨狀態 0 和 1 設置的觸發器。為此有兩個輸入:

- S——集合(集合);

- R - 重置。

有一個直接輸出Q,也可以是反相輸出Q1。它的邏輯電平總是與 Q 相反——這在設計電路時很有用。

當對輸入 S 施加正電平時,輸出 Q 將設置為邏輯 1(如果有反向輸出,它將變為電平 0)。之後設置輸入上的信號可以隨心所欲地改變 - 輸出電平不會受到影響。只要那個出現在R輸入上。這會將觸發器設置為狀態 0(反向引腳上的 1)。復位輸入上的信號變化不會影響元件的進一步狀態。

重要的! 禁止在兩個輸入上都有邏輯 1 的變體。觸發器將設置為任意狀態。在設計電路時應避免這種情況。

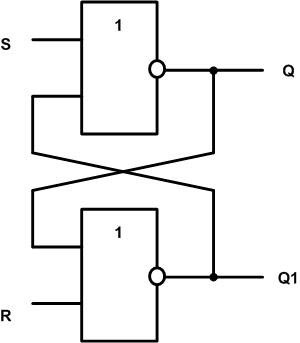

RS 觸發器可以基於常用的雙輸入 I-NE 元件構建。這種方法在傳統芯片以及可編程陣列內部都是可行的。

一個或兩個輸入可以反轉。這意味著在這些引腳上,觸發器由低電平而不是高電平的外觀控制。

如果您使用兩個 I-NE 輸入元件構建 RS 觸發器,則兩個輸入都將反轉 - 由邏輯零的電源控制。

RS 觸發器有一個門控版本。它有一個額外的 C 輸入。當滿足兩個條件時發生切換:

- Set 或 Reset 輸入上存在高電平;

- 時鐘信號的存在。

當需要延遲切換時使用這種元件,例如,在瞬態結束時。

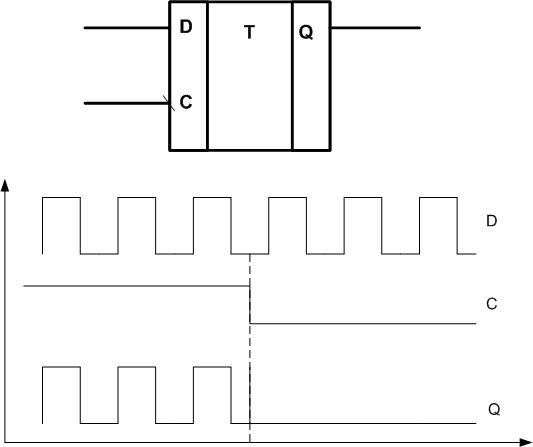

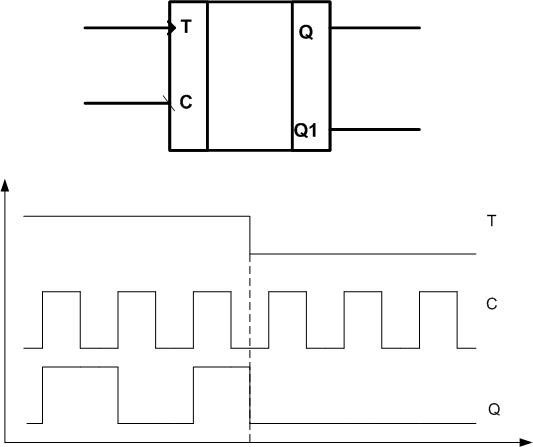

D-觸發器

D-trigger(“透明觸發器”,“latch”)屬於同步器件的範疇,時鐘在輸入C上。還有一個用於數據D(Data)的輸入。就功能而言,該設備屬於通過一個輸入接收信息的觸發器。

只要時鐘輸入端存在邏輯 1,輸出端 Q 的信號就會重複數據輸入端的信號(透明模式)。一旦選通電平變為 0,輸出 Q 的電平保持與下降(鎖定)時的電平相同。這樣,您可以在任何時間點將輸入電平鎖定到輸入。還有邊沿觸發的 D 觸發器。它們在選通脈衝的上升沿鎖存信號。

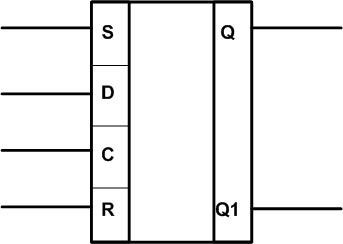

在實踐中,兩種雙穩態器件可以組合在一個芯片中。例如,D 和 RS 觸發器。在這種情況下,設置/復位輸入優先。如果它們的邏輯為零,則該元素的行為類似於正常的 D 觸發器。如果至少有一個輸入為高電平,則無論輸入 C 和 D 上的信號如何,輸出都設置為 0 或 1。

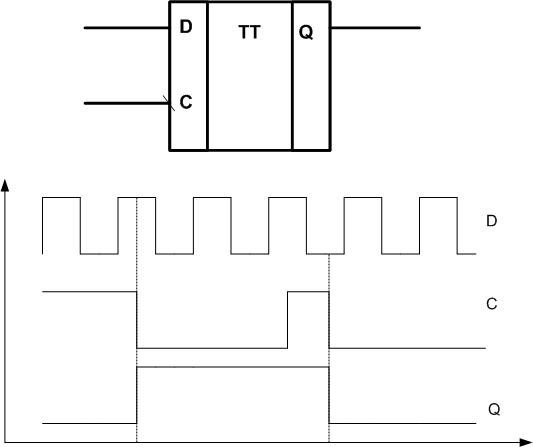

D-觸發器的透明度並不總是一個有用的功能。為避免這種情況,使用了雙元素(觸發器觸發器)並用字母 TT 表示。第一個觸發器是一個正常的鎖存器,它允許輸入信號進入輸出。第二個觸發器是記憶元件。兩者都由一個閃光燈計時。

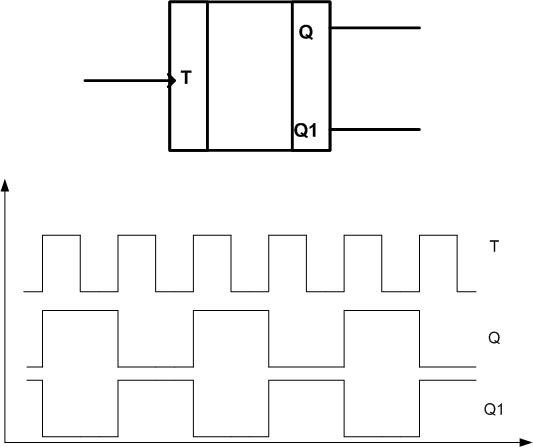

T-觸發器

T觸發器是一個可數的雙穩態元件。它的工作邏輯很簡單,每次下一個邏輯輸入出現時它都會改變狀態。如果將脈衝信號應用於其輸入,則輸出頻率將是輸入頻率的兩倍。在反向輸出上,信號將與正向信號反相。

這就是異步 T 觸發器的工作原理。還有一個同步版本。當脈衝信號施加到時鐘輸入並且引腳 T 出現邏輯信號時,該元件的行為方式與異步信號相同 - 它將輸入頻率分成兩半。如果 T 引腳為邏輯零,則無論是否存在門,Q 輸出都設置為低電平。

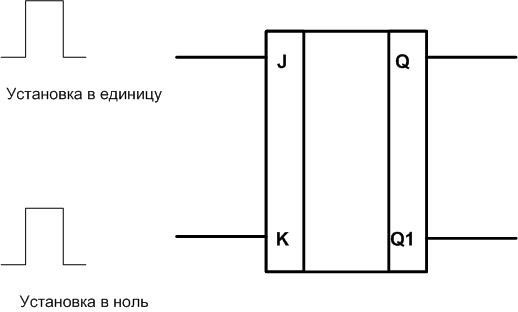

JK 觸發器

JK 觸發器

這種雙穩態元素屬於通用範疇。它可以通過輸入單獨控制。 JK 觸發器的邏輯與 RS 元素的邏輯相似。 J(作業)輸入用於將輸出設置為 1。引腳 K(保持)上的高電平將輸出重置為零。 RS 觸發器的根本區別在於兩個控制輸入上同時出現一個是不被禁止的。在這種情況下,元素的輸出將其狀態更改為相反。

如果連接了 Job 和 Keep 輸出,則 JK 觸發器變為異步計數 T 觸發器。當對組合輸入應用曲折時,輸出將是頻率的一半。與 RS 元素一樣,有一個 JK 觸發器的時鐘版本。在實踐中,主要使用這種類型的門控元件。

實際使用

即使外部信號被去除,觸發器也能保留記錄信息的特性允許它們用作容量為 1 位的存儲單元。可以從單個元素構建矩陣以存儲二進制狀態 - 這是用於構建靜態隨機存取存儲器 (SRAM) 的原理。這種存儲器的一個特點是電路簡單,不需要額外的控制器。因此 SRAM 用於控制器和 PLC。但低寫入密度阻礙了此類矩陣在 PC 和其他強大的計算系統中的使用。

上面提到了使用觸發器作為分頻器。雙穩態元素可以連接成鏈來獲得不同的劃分因子。相同的鏈可用作脈衝計數器。為此,有必要從中間元件讀取每個時刻的輸出狀態 - 我們得到一個二進制代碼,對應於到達第一個元件輸入的脈衝數。

根據使用的觸發器的類型,計數器可以是同步的或異步的。順序代碼到並行代碼的轉換器使用相同的原理,但這裡只使用可以門控的元素。觸發器還用於構建數字延遲線和其他二進制元素。

RS 觸發器用作電平鎖存器(接觸反彈抑制器)。如果使用機械開關(按鈕、開關)作為邏輯電平源,按下時顫振效果會形成許多信號代替一個信號。 RS-trigger 成功地解決了這個問題。

雙穩態器件的應用領域廣泛。在他們的幫助下可以解決的任務範圍在很大程度上取決於設計師的想像力,尤其是在非標準解決方案領域。

相關文章: